# LYF89023 100V, 3A Step-Down converter with ultra low IQ

#### 1 Features

- Wide input voltage range of 5V to 100V

- Junction temperature range: –40°C to +150°C

- · Fixed 3ms internal soft start timer

- Peak and valley current limit protection

- EN UVLO and thermal shutdown protection

- Low minimum on and off times of 100ns/200ns

- Adjustable switching frequency up to 500kHz

- 5µA shutdown quiescent current CC

- · COT mode control architecture

- Integrated  $0.325\Omega$  NFET buck switch supports wide duty cycle range

- 1.2V internal voltage reference

- No loop compensation components

- Internal VCC bias regulator and boot diode

- Open drain power good indicator

- ESOP8 package

#### 2 Applications

- Appliances, power and garden tools

- High-cell-count battery packs (E-Bike, E-Scooter)

- · Motor drives, drones, telecom

#### 3 Description

The LYF89023 asynchronous buck converter is designed to regulate over a wide input voltage range, minimizing the need for external surge suppression components. A minimum controllable on time of 100ns facilitates large step down conversion ratios, enabling the direct step down from a 48V nominal input to low-voltage rails for reduced system complexity and solution cost. The LYF89023 operates during input voltage dips as low as 5V, at nearly 100% duty cycle if needed, making it an excellent choice for wide input supply range industrial and high cell count battery pack applications.

With integrated high side power MOSFET, the LYF89023 delivers up to 3A of output current. A constant on time (COT) control architecture provides nearly constant switching frequency with excellent load and line transient response. Additional features of the LYF89023 include ultra low IQ and high light load efficiency, innovative peak and valley over current protection, integrated VCC bias supply and bootstrap diode, precision enable and input UVLO, and thermal shutdown protection with automatic recovery. An open drain PGOOD indicator provides sequencing, fault reporting, and output voltage monitoring.

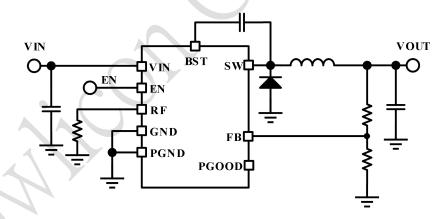

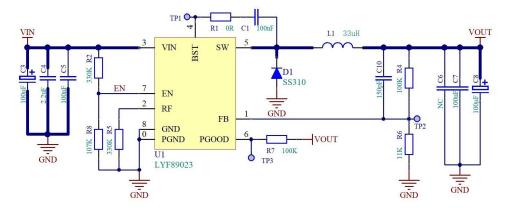

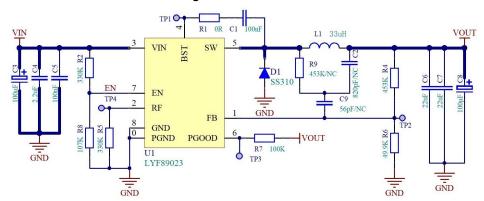

## **4 Typical Application Schematic**

Fig. 4-1 Typical Application Schematic

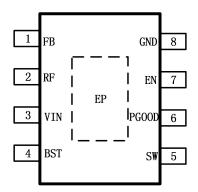

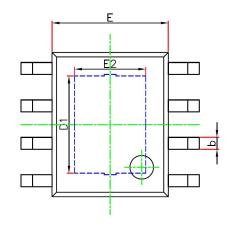

# **5 Pin Configuration and Functions**

Fig. 5-1 Pin-Function

| Pin     |         | Description                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Number  | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 1       | FB      | Feedback input of voltage regulation comparator.                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 2       | RF      | On time programming pin. A resistor between this pin and GND sets the buck switch on time.                                                                                                                                                                                                                                                                                                              |  |  |

| 3       | VIN     | Regulator supply input pin to high side power MOSFET and internal bias regulator. Connect directly to the input supply of the buck converter with short, low impedance paths.                                                                                                                                                                                                                           |  |  |

| 4       | BST     | Bootstrap gate drive supply.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 5       | SW      | Switching node that is internally connected to the source of the high side NMOS buck switch and the drain of the low side NMOS synchronous rectifier. Connect to the switching node of the power inductor.                                                                                                                                                                                              |  |  |

| 6 PGOOD |         | Power good indicator. This pin is an open drain output pin. Connect to a source voltage                                                                                                                                                                                                                                                                                                                 |  |  |

|         |         | through an external pull up resistor between 10kΩ to 100kΩ                                                                                                                                                                                                                                                                                                                                              |  |  |

| 7       | EN/UVLO | Precision enable and under voltage lockout (UVLO) programming pin. If the EN/UVLO voltage is below 1.1V, the converter is in the shutdown mode with all functions disabled. If the UVLO voltage is greater than 1.1V and below 1.5V, the converter is in standby mode with the internal VCC regulator operational and no switching. If the EN/UVLO voltage is above 1.5V, the start up sequence begins. |  |  |

| 8       | GND     | Ground connection for internal circuits                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 9       | EP      | Exposed pad of the package. No internal electrical connection. Solder the EP to the GND pin and connect to a large copper plane to reduce thermal resistance.                                                                                                                                                                                                                                           |  |  |

# 6 Device Marking Information

| Part Number | Order Information | Package | Package Qty | Top Marking     |

|-------------|-------------------|---------|-------------|-----------------|

| LYF89023    | LYF89023IES08A    | ESOP8   | 4000        | 89023<br>RAAYMD |

89023:Part Number

RAAYMD: RAA: LOT NO.; YMD: Package Date Code

## 7 Specifications

## 7.1 Absolute Maximum Ratings(Note1)

| PARAMETER    | MIN  | MAX   | Unit |

|--------------|------|-------|------|

| VIN to GND   | -0.3 | 100   |      |

| EN to GND    | -0.3 | 100   |      |

| FB to GND    | -0.3 | 5.5   |      |

| RF to GND    | -0.3 | 5.5   | V    |

| BST to GND   | -0.3 | 105.5 | V    |

| BST to SW    | -0.3 | 5.5   |      |

| SW to GND    | -1.5 | 100   |      |

| PGOOD to GND | -0.3 | 100   |      |

## 7.2 Handling Ratings

| PARAMET          | ER DEFINITION             | MIN | MAX  | UNIT |

|------------------|---------------------------|-----|------|------|

| T <sub>ST</sub>  | Storage Temperature Range | -65 | 150  | °C   |

| TJ               | Junction Temperature      | -40 | +150 | °C   |

| V <sub>ESD</sub> | HBM Human body model      |     | 2    | kV   |

## 7.3 Recommended Operating Conditions (Note 2)

|                | PARAMETER                                            | MIN | MAX  | Unit |

|----------------|------------------------------------------------------|-----|------|------|

| Input Voltages | VIN                                                  | 5.0 | 100  | V    |

| Temperature    | Operating junction temperature range, T <sub>J</sub> | -40 | +150 | °C   |

## 7.4 Thermal Information(Note 3)

| Symbol          | Description                            | ESOP8 | Unit |

|-----------------|----------------------------------------|-------|------|

| θ <sub>JA</sub> | Junction to ambient thermal resistance | 41.1  |      |

| θυς             | Junction to case thermal resistance    | 37.3  | °C/W |

| θЈВ             | Junction to board thermal resistance   | 30.6  |      |

- Exceeding these ratings may damage the device.

The device function is not guaranteed outside of the recommended operating conditions.

- 3) Measured on approximately 1" square of 1 oz copper.

## 7.5 Electrical Characteristics

Typical values correspond to TJ =  $25^{\circ}$ C. Minimum and maximum limits apply over the full  $-40^{\circ}$ C to  $150^{\circ}$ C junction temperature range unless otherwise indicated. VIN = 24 V and VEN/UVLO = 2 V unless otherwise stated.

| Supply voltages         | PARAMETER                                  | CONDITION                 | MIN   | TYP   | MAX   | UNIT |  |  |

|-------------------------|--------------------------------------------|---------------------------|-------|-------|-------|------|--|--|

| I <sub>Q-SHUTDOWN</sub> | VIN shutdown current                       | V <sub>EN</sub> = 0 V     |       | 5     | 10    | uA   |  |  |

| I <sub>Q-ACTIVE</sub>   | VIN active current                         | V <sub>EN</sub> = 2.5 V   |       | 330   | 400   | uA   |  |  |

| UVLO/EN                 |                                            |                           |       |       |       |      |  |  |

| V <sub>SD-RISING</sub>  | Shutdown threshold                         | V <sub>EN</sub> rising    |       |       | 1.1   | V    |  |  |

| V <sub>SD-FALLING</sub> | Shutdown threshold                         | V <sub>EN</sub> falling   | 0.45  |       |       | V    |  |  |

| V <sub>EN-RISING</sub>  | Enable threshold                           | V <sub>EN</sub> rising    | 1.45  | 1.5   | 1.55  | V    |  |  |

| V <sub>EN-FALLING</sub> | Enable threshold                           | V <sub>EN</sub> falling   | 1.35  | 1.4   | 1.44  | V    |  |  |

| FEEDBACK                |                                            |                           |       |       |       |      |  |  |

| $V_{REF}$               | FB regulation voltage                      | V <sub>FB</sub> falling   | 1.18  | 1.2   | 1.218 | V    |  |  |

| FREQUNEC                |                                            |                           |       |       |       |      |  |  |

| Freq1                   |                                            | RrF=200kΩ                 |       | 500   |       | kHz  |  |  |

| Freq2                   |                                            | RRF=330kΩ                 |       | 300   |       | kHz  |  |  |

| Freq3                   |                                            | Rrf=500kΩ                 |       | 200   |       | kHz  |  |  |

| PGOOD                   |                                            |                           |       |       |       |      |  |  |

| V <sub>PG-UTH</sub>     | FB upper threshold for PGOOD high to low   | V <sub>FB</sub> rising    | 1.105 | 1.14  | 1.175 | V    |  |  |

| $V_{PG-LTH}$            | FB lower threshold for PGOOD high to low   | V <sub>FB</sub> falling   | 1.055 | 1.08  | 1.1   | V    |  |  |

| V <sub>PG-HYS</sub>     | PGOOD upper and lower threshold hysteresis | V <sub>FB</sub> falling   |       | 60    |       | mV   |  |  |

| R <sub>PG</sub>         | PGOOD pull down resistance                 | V <sub>FB</sub> = 1 V     |       | 200   |       | Ω    |  |  |

| BOOTSTRAP               |                                            |                           |       |       |       |      |  |  |

| V <sub>BST-UV</sub>     | Gate drive UVLO                            | V <sub>BST</sub> rising   |       | 2.7   | 3.4   | ٧    |  |  |

| POWER SWITCHE           | :S                                         | •                         | ·     |       |       |      |  |  |

| R <sub>DSON-HS</sub>    | High-side MOSFET RDSON                     | I <sub>SW</sub> = -100 mA |       | 0.325 |       | Ω    |  |  |

| SOFT START              | SOFT START                                 |                           |       |       |       |      |  |  |

| tss                     | Internal soft-start time                   |                           | 1.75  | 3     | 4.75  | ms   |  |  |

| CURRENT LIMIT           |                                            |                           |       |       |       |      |  |  |

| Іреак                   | Peak current limit threshold (HS)          |                           |       | 4.0   | 4.15  | Α    |  |  |

| THERMAL SHUTE           | OOWN                                       |                           |       |       |       |      |  |  |

| TSD                     | Thermal shutdown threshold                 | TJ rising                 |       | 175   |       | °C   |  |  |

| TSD-HYS                 | Thermal shutdown hysteresis                |                           |       | 10    |       | °C   |  |  |

|                         |                                            | •                         |       |       |       |      |  |  |

## LYF89023

LYF89023

## 9 Detailed Descriptions

#### 9.1 Overview

The LYF89023 is an easy to use, ultra low IQ constant on time (COT) asynchronous step down buck regulator. With integrated high side power MOSFET, the LYF89023 is a low cost, highly efficient buck converter that operates from a wide input voltage of 5V to 100V, delivering up to 3A DC load current. The LYF89023 is available in the ESOP8 package. This constant on time (COT) converter is ideal for low noise, high current, and fast load transient requirements, operating with a predictive on time switching pulse. Over the input voltage range, input voltage feed forward is employed to achieve a quasi fixed switching frequency. A controllable on time as low as 100ns permits high step down ratios and a minimum forced off time of 200ns provides extremely high duty cycles allowing VIN to drop close to VOUT before frequency fold back occurs. At light loads the device transitions into an ultra low IQ mode to maintain high efficiency and prevent draining battery cells connected to the input when the system is in standby. The LYF89023 implements a smart peak and valley current limit detection circuit to ensure robust protection during output short circuit conditions. Control loop compensation is not required for this regulator, reducing design time and external component count. The LYF89023 incorporates additional features for comprehensive system requirements, including an open drain Power Good circuit for power rail sequencing and fault reporting, internally fixed soft start, monotonic start up into prebiased loads, smart cycle by cycle current limit for optimal inductor sizing, and thermal shutdown with automatic recovery. These features enable a flexible and easy to use platform for a wide range of applications. The LYF89023 supports a wide range of endequipment systems requiring a regulated output from a high input supply where the transient voltage deviates from its DC level. Examples of such end equipment systems are 48V automotive systems, high cell count battery pack systems, 24V industrial systems, and 48V telecom and PoE voltage ranges. The pin arrangement is designed for a simple layout requiring only a few external components.

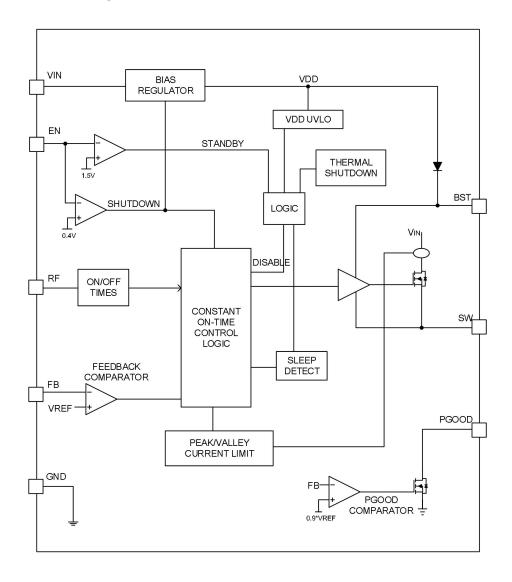

#### 9.2 Functional Block Diagram

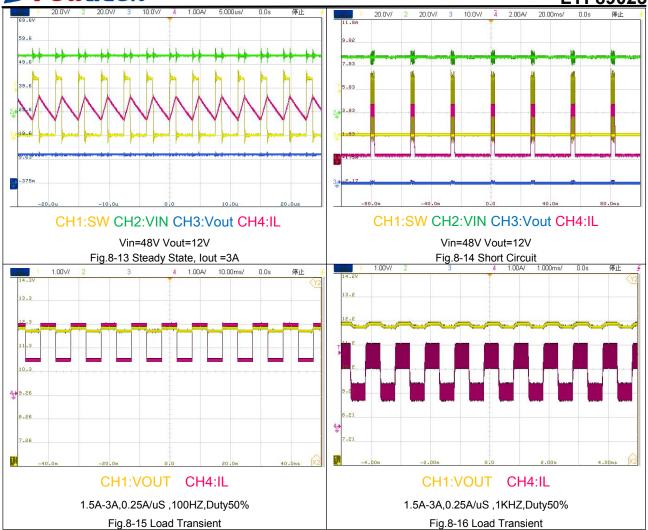

#### 9.3 Control Architecture

The LYF89023 step down switching converter employs a constant on time (COT) control scheme. The COT control scheme sets a fixed on time  $t_{\text{ON}}$  of the high side FET using a timing resistor (RON). The  $t_{\text{ON}}$  is adjusted as Vin changes and is inversely proportion to input voltage to maintain a fixed frequency when in continuous conduction mode (CCM). After expiration of  $t_{\text{ON}}$ , the high side FET remains off until the feedback pin is equal or below the reference voltage of 1.2V. In order to maintain stability, the feedback comparator requires a minimal ripple voltage that is in phase with the inductor current during the off time. Furthermore, this change in feedback voltage during the off time must be large enough to dominate any noise present at the feedback node. The minimum recommended ripple voltage is 20mV. Refer to *Table* 9-3-1 for different types of ripple injection schemes that ensure stability over the full input voltage range. During a rapid start up or a positive load step, the regulator operates with minimum off times until regulation is achieved. This feature enables extremely fast load transient response with minimum output voltage undershoot. When regulating the output in steady state operation, the off time automatically adjusts itself to produce the SW pin duty cycle required for output voltage regulation to maintain a fixed switching frequency.

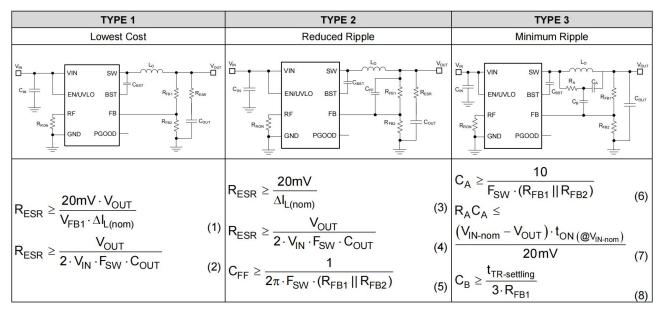

Table 9-3-1. Ripple Generation Methods

**Table 9-3-1** presents 3 different methods for generating appropriate voltage ripple at the feedback node. Type-1 ripple generation method uses a single resistor, R<sub>ESR</sub> in series with the output capacitor. The generated voltage ripple has two components, capacitive ripple caused by the inductor ripple current charging and discharging the output capacitor and resistive ripple caused by the inductor ripple current flowing into the output capacitor and through series resistance R<sub>ESR</sub>. The capacitive ripple component is out of phase with the inductor current and does not decrease monotonically during the off time. The resistive ripple component is in phase with the inductor current and decreases monotonically during the off time. The resistive ripple must exceed the capacitive ripple at VOUT for stable operation. If this condition is not satisfied, unstable switching behavior is observed in COT converters, with multiple on time bursts in close succession followed by a long off time. **Equation 1** and **Equation 2** define the value of the series resistance R<sub>ESR</sub> to ensure sufficient in phase ripple at the feedback node.

Type-2 ripple generation uses a  $C_{FF}$  capacitor in addition to the series resistor. As the output voltage ripple is directly AC coupled by  $C_{FF}$  to the feedback node, the  $R_{ESR}$  and ultimately the output voltage ripple are reduced by a factor of  $V_{OUT}$  /  $V_{FB1}$ .

Type-3 ripple generation uses an RC network consisting of  $R_A$  and  $C_A$ , and the switch node voltage to generate a triangular ramp that is in phase with the inductor current. This triangular wave is the AC coupled into the feedback node with capacitor  $C_B$ . Because this circuit does not use output voltage ripple, it is suited for applications where low output voltage ripple is critical.

#### 9.4 Internal VCC Regulator and Bootstrap Capacitor

The LYF89023 contains an internal linear regulator that is powered from VIN with a nominal output of 5V, eliminating the need for an external capacitor to stabilize the linear regulator. The internal VCC regulator supplies current to internal circuit blocks including FET driver and logic circuits. The input pin (VIN) can be connected directly to line voltages up to 100V. As the power MOSFET has a low total gate charge, use a low bootstrap capacitor value to reduce the stress on the internal regulator. It is required to select a high quality 2.2nF 50V X7R ceramic bootstrap capacitor as specified in the Absolute Maximum Ratings. Selecting a higher value capacitance stresses the internal VCC regulator and damages the device. A lower capacitance than required may not be sufficient to drive the internal gate of the power MOSFET. An internal diode connects from the linear regulator to the BST pin to replenish the charge in the high side gate drive bootstrap capacitor when the SW voltage is low.

## 9.5 Regulation Comparator

The feedback voltage at FB is compared to an internal 1.2V reference. The LYF89023 voltage regulation loop regulates the output voltage by maintaining the FB voltage equal to the internal reference voltage,  $V_{REF}$ . A resistor divider programs the ratio from output voltage  $V_{OUT}$  to FB. For a target  $V_{OUT}$  set point, calculate  $R_{FB2}$  based on the selected  $R_{FB1}$  using **Equation 9.**

$$R_{FB2} = \frac{1.2V}{V_{OUT} - 1.2V} \times R_{FB1}$$

(9)

Recommending selecting  $R_{FB1}$  in the range of  $100k\Omega$  to  $1M\Omega$  for most applications. A larger  $R_{FB1}$  consumes less DC current, which is mandatory if light load efficiency is critical.  $R_{FB1}$  larger than  $1M\Omega$  is not recommended as the feedback path becomes more susceptible to noise. It is important to route the feedback trace away from the noisy area of the PCB and keep the feedback resistors close to the FB pin.

#### 9.6 Internal Soft Start

The LYF89023 employs an internal soft start control ramp that allows the output voltage to gradually reach a steady state operating point, thereby reducing start up stresses and current surges. The soft start feature produces a controlled, monotonic output voltage start up. The soft start time is internally set to 3ms.

#### 9.7 Adjustable Switching Frequency

Determine the RRF resistor using *Equation 10* to set a specific switching frequency in CCM.

$$F_{SW}(kHz) = \frac{100000}{R_{RF}(k\Omega)}$$

(10)

#### 9.8 Enable/Under voltage Lockout (EN/UVLO)

The LYF89023 contains a dual level EN/UVLO circuit. When the EN/UVLO voltage is below 1.1V (typical), the converter is in a low current shutdown mode and the input quiescent current (IQ) is dropped down to 5µA. When the voltage is greater than 1.1V but less than 1.5V (typical), the converter is in standby mode. In standby mode the internal bias regulator is active while the control circuit is disabled. When the voltage exceeds the rising threshold of 1.5V (typical), normal operation begins. Install a resistor divider from VIN to GND to set the minimum operating voltage of the regulator.

### 9.9 Power Good (PGOOD)

The LYF89023 provides a PGOOD flag pin to indicate when the output voltage is within the regulation level. Use the PGOOD signal for start up sequencing of downstream converters or for fault protection and output monitoring. PGOOD is an open drain output that requires a pull up resistor to a DC supply. The typical range of pull up resistance is  $10k\Omega$  to  $100k\Omega$ . When the FB voltage exceeds 95% of the internal reference  $V_{REF}$ , the internal PGOOD switch turns off and PGOOD can be pulled high by the external pull up. If the FB voltage falls below 90% of  $V_{REF}$ , an internal  $25\Omega$  PGOOD switch turns on and PGOOD is pulled low to indicate that the output voltage is out of regulation. The rising edge of PGOOD has a built in deglitch delay of  $5\mu$ s.

#### 9.10 Thermal Protection

The LYF89023 includes an internal junction temperature monitor to protect the device in the event of a higher than normal junction temperature. If the junction temperature exceeds 175°C (typical), thermal shutdown occurs to prevent further power dissipation and temperature rise. The LYF89023 initiates a restart sequence when the junction temperature falls to 165°C, based on a typical thermal shutdown hysteresis of 10°C. This is a nonlatching protection, and, as such, the device cycles into and out of thermal shutdown if the fault persists.

#### 10 Applications and Implementation

#### 10.1 Selecting the Inductor

The operating frequency and inductor selection are interrelated in that higher operating frequencies allow the use of smaller inductor and capacitor values. The inductor value has a direct effect on ripple current.

For a given ripple, the inductance terms in continuous mode are as Equation 11.

$$L = \frac{V_{\text{OUT}}}{f_{\text{e}} \times \Delta I_{\text{I}}} \left( 1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right) \tag{11}$$

where: f<sub>s</sub> is operating frequency, kHz

∆I<sub>L</sub> is maximum inductor ripple current, A, usually select 20~40% maximum output current.

For high efficiency, choose an inductor with low core loss, such as ferrite. Also, the inductor should have low DC resistance to reduce the I<sup>2</sup>R losses, and must be able to handle the peak inductor current without saturating. To minimize radiated noise, use a toroid, pot core or shielded bobbin inductor.

#### 10.2 Output Rectifier Diode

The output rectifier diode supplies current to the inductor when the high-side switch is off. To reduce losses due to the diode forward voltage and recovery times, use a Schottky diode.

The average current through the diode can be approximated with *Equation12*.

$$I_{\rm D} = I_{\rm OUT} \times (1 - \frac{V_{\rm OUT}}{V_{\rm VIN}})$$

(12)

Choose a diode with a maximum reverse voltage rating greater than the maximum input voltage and a current rating is greater than the average diode current.

#### 10.3 Output Capacitor (Cout)

Select a ceramic output capacitor to limit the capacitive voltage ripple at the converter output. This is the sinusoidal ripple voltage that is generated from the triangular inductor current ripple flowing into and out of the capacitor. Select an output capacitance using *Equation13* to limit the voltage ripple component to 0.5% of the output voltage.  $C_{OUT} \geq \frac{\Delta I_L}{8 \times F_{SW} \times V_{OUT(ripple)}}$

$$C_{OUT} \ge \frac{\Delta I_L}{8 \times F_{SW} \times V_{OUT(ripple)}} \tag{13}$$

Substituting  $\Delta I_{L(nom)}$  of 447mA gives  $C_{OUT}$  greater than 3.1µF. With voltage coefficients of ceramic capacitors taken in consideration, a 22µF, 25V rated capacitor with X7R dielectric is selected.

#### 10.4 Input Capacitor (C<sub>IN</sub>)

An input capacitor is necessary to limit the input ripple voltage while providing AC current to the buck power stage at every switching cycle. To minimize the parasitic inductance in the switching loop, position the input capacitors as close as possible to the VIN and GND pins of the LYF89023. The input capacitors conduct a square wave current of peak to peak amplitude equal to the output current. It follows that the resultant capacitive component of AC ripple voltage is a triangular waveform. Together with the ESR related ripple component, the peak-to-peak ripple voltage amplitude is given by Equation14.

$$V_{\text{IN(ripple)}} = \frac{I_{\text{OUT}} \times D \times (1 - D)}{F_{\text{SW}} \times C_{\text{IN}}} + I_{\text{OUT}} \times R_{\text{ESR}}$$

(14)

The input capacitance required for a load current, based on an input voltage ripple specification (ΔVIN), is given by Equation15:

$$C_{IN} \ge \frac{I_{OUT} \times D \times (1-D)}{F_{SW} \times (V_{IN(ripple)} - I_{OUT} \times R_{ESR})}$$

(15)

The recommended high-frequency input capacitance is 2.2µF or higher. Ensure the input capacitor is a high quality X7S or X7R ceramic capacitor with sufficient voltage rating for C<sub>IN</sub>. Based on the voltage coefficient of ceramic capacitors, choose a voltage rating of twice the maximum input voltage. Additionally, some bulk capacitance is required if the LYF89023 is not located within approximately 5cm from the input voltage source. This capacitor provides parallel damping to the resonance associated with parasitic inductance of the supply lines and high Q ceramics.

### 11 PCB Layout

#### 11.1 Guideline

Layout is a critical portion of good power supply design. The following guidelines will help users design a PCB with the best power conversion performance, thermal performance, and minimized generation of unwanted EMI.

- Place the input decoupling capacitor, catch diode, and the LYF89023 (VIN, SW, and GND) as close to each other as possible.

- 2. Keep the power traces very short and fairly wide, especially for the SW node. This can help greatly reduce voltage spikes on the SW node and lower the EMI noise level.

- 3. Run the feedback trace as far from the inductor and noisy power traces (like the SW node) as possible.

- 4. Place thermal vias with 15mil barrel diameter and 40mil pitch (distance between the centers) under the exposed pad to improve thermal conduction.

#### 11.2 Application Examples

Fig. 11-2-1 Schematic

Fig. 11-2-2 Schematic

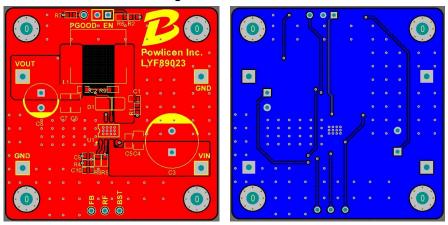

Fig. 11-2-3 PCB

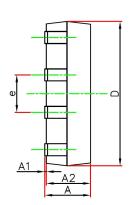

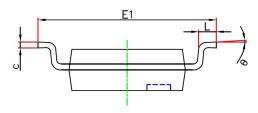

## 12 Packaging Information

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |  |

|--------|---------------------------|-------|----------------------|-------|--|

| Symbol | Min.                      | Max.  | Min.                 | Max.  |  |

| Α      | 1.300                     | 1.700 | 0.051                | 0.067 |  |

| A1     | 0.000                     | 0.100 | 0.000                | 0.004 |  |

| A2     | 1.350                     | 1.550 | 0.053                | 0.061 |  |

| b      | 0.330                     | 0.510 | 0.013                | 0.020 |  |

| С      | 0.170                     | 0.250 | 0.007                | 0.010 |  |

| D      | 4.700                     | 5.100 | 0.185                | 0.201 |  |

| D1     | 3.202                     | 3.402 | 0.126                | 0.134 |  |

| E      | 3.800                     | 4.000 | 0.150                | 0.157 |  |

| E1     | 5.800                     | 6.200 | 0.228                | 0.244 |  |

| E2     | 2.313                     | 2.513 | 0.091                | 0.099 |  |

| е      | 1.270(BSC)                |       | 0.050(               | (BSC) |  |

| L      | 0.400                     | 1.270 | 0.016                | 0.050 |  |

| θ      | 0°                        | 8°    | 0°                   | 8°    |  |

#### **IMPORTANT NOTICE**

Powlicon Microelectronics Co., Ltd. assumes no responsibility for any error which may appear in this document. Powlicon Microelectronics Co., Ltd. reserves the right to change devices or specifications detailed herein at any time without notice. Powlicon Microelectronics Co., Ltd. does not assume any liability arising out of the application or use of any product described herein; neither it does it convey any license under its patent rights, nor the rights of others. Powlicon Microelectronics Co., Ltd. products are not authorized for use as critical components in life support devices or systems without written approval letter from the Chief Executive Officer of Powlicon Microelectronics Co., Ltd. The use of products in such applications shall assume all risks of such use and will agree to not hold against Powlicon Microelectronics Co., Ltd. for any damage.